# aPR33A1 / aPR33A2 / aPR33A3

# Fixed 1/ 2/ 4/ 8 Message Mode (C2.1)

# **Datasheet**

## **Recording voice IC**

## **APLUS INTEGRATED CIRCUITS INC.**

#### Address:

3 F-10, No. 32, Sec. 1, Chenggung Rd., Taipei, Taiwan 115, R.O.C.

#### TEL:

886-2-2782-9266

## FAX:

886-2-2782-9255

#### **WEBSITE:**

http://www.aplusinc.com.tw

## **Technology E-mail:**

service@aplusinc.com.tw

#### Sales E-mail:

sales@aplusinc.com.tw

#### ■ FEATURES

- Operating Voltage Range: 3V ~ 6.5V

- Single Chip, High Quality Audio/Voice Recording & Playback Solution

- No External ICs Required

- Minimum External Components

- User Friendly, Easy to Use Operation

- Programming & Development Systems Not Required

- 170/340/680 sec. Voice Recording Length in aPR33A1/aPR33A2/aPR33A3

- Powerful 16-Bits Digital Audio Processor.

- Nonvolatile Flash Memory Technology

- No Battery Backup Required

- External Reset pin.

- Powerful Power Management Unit

- Very Low Standby Current: 1uA

- ◆ Low Power-Down Current: 15uA

- Supports Power-Down Mode for Power Saving

- Built-in Audio-Recording Microphone Amplifier

- ◆ No External OPAMP or BJT Required

- Easy to PCB layout

- Configurable analog interface

- Differential-ended MIC pre-amp for Low Noise

- High Quality Line Receiver

- High Quality Analog to Digital, DAC and PWM module

- Resolution up to 16-bits

- Simple And Direct User Interface

- Averagely 1,2,4 or 8 voice messages record & playback

#### DESCRIPTION

Today's consumers demand the best in audio/voice. They want crystal-clear sound wherever they are in whatever format they want to use. APLUS delivers the technology to enhance a listener's audio/voice experience.

The aPR33A series are powerful audio processor along with high performance audio analog-to-digital converters (ADCs) and digital-to-analog converters (DACs). The aPR33A series are a fully integrated solution offering high performance and unparalleled integration with analog input, digital processing and analog output functionality. The aPR33A series incorporates all the functionality required to perform demanding audio/voice applications. High quality audio/voice systems with lower bill-of-material costs can be implemented with the aPR33A series because of its integrated analog data converters and full suite of quality-enhancing features such as sample-rate convertor.

The aPR33A series C2.0 is specially designed for simple key trigger, user can record and playback the message averagely for 1, 2, 4 or 8 voice message(s) by switch, It is suitable in simple interface or need to limit the length of single message, e.g. toys, leave messages system, answering machine etc. Meanwhile, this mode provides the power-management system. Users can let the chip enter power-down mode when unused. It can effectively reduce electric current consuming to 15uA and increase the using time in any projects powered by batteries.

Ver. C 3/27 2/19/2013

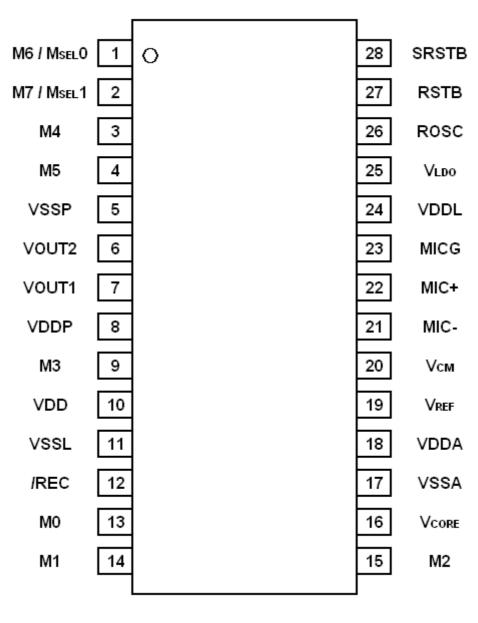

## PIN CONFIGURATION

**SOP Package**

Ver. C 4/27 2/19/2013

## **■ PIN DESCRIPTION**

| Pin Names  | Pin No | TYPE   | Description                                     |  |  |  |  |  |

|------------|--------|--------|-------------------------------------------------|--|--|--|--|--|

| VDDP       | 8      |        |                                                 |  |  |  |  |  |

| VDD        | 10     |        | Decitive never comply                           |  |  |  |  |  |

| VDDA       | 18     |        | Positive power supply.                          |  |  |  |  |  |

| VDDL       | 24     |        |                                                 |  |  |  |  |  |

| VSSP       | 5      |        |                                                 |  |  |  |  |  |

| VSSL       | 11     |        | Power ground.                                   |  |  |  |  |  |

| VSSA       | 17     |        |                                                 |  |  |  |  |  |

| VLDO       | 25     |        | Internal LDO output.                            |  |  |  |  |  |

| Vcore      | 16     |        | Positive power supply for core.                 |  |  |  |  |  |

| VREF       | 19     |        | Reference voltage.                              |  |  |  |  |  |

| Vсм        | 20     |        | Common mode voltage.                            |  |  |  |  |  |

| Rosc       | 26     | INPUT  | Oscillator resistor input.                      |  |  |  |  |  |

| RSTB       | 27     | INPUT  | Reset. (Low active)                             |  |  |  |  |  |

| SRSTB      | 28     | INPUT  | System reset, pull-down a resistor to the VSSL. |  |  |  |  |  |

| MIC+       | 21     | INPUT  | Migraphone differential input                   |  |  |  |  |  |

| MIC-       | 22     | INPUT  | Microphone differential input.                  |  |  |  |  |  |

| MICG       | 23     | OUTPUT | Microphone ground.                              |  |  |  |  |  |

| VOUT1      | 7      | INPUT  | PWM output to drive speaker directly.           |  |  |  |  |  |

| VO011      |        |        | DAC option.                                     |  |  |  |  |  |

| VOUT2      | 6      | INPUT  | PWM output to drive speaker directly.           |  |  |  |  |  |

| VO012      |        |        | DAC output.                                     |  |  |  |  |  |

| /REC       | 12     | INPUT  | Record Mode. (Low active)                       |  |  |  |  |  |

| M0         | 13     | INPUT  | Message-0.                                      |  |  |  |  |  |

| M1         | 14     | INPUT  | Message-1.                                      |  |  |  |  |  |

| M2         | 15     | INPUT  | Message-2.                                      |  |  |  |  |  |

| M3         | 9      | INPUT  | Message-3.                                      |  |  |  |  |  |

| M4         | 3      | INPUT  | Message-4.                                      |  |  |  |  |  |

| M5         | 4      | INPUT  | Message-5.                                      |  |  |  |  |  |

| M6 / Msel0 | 1      | INPUT  | Message-6, Message select 0.                    |  |  |  |  |  |

| M7 / Msel1 | 2      | INPUT  | Message-7, Message select 1.                    |  |  |  |  |  |

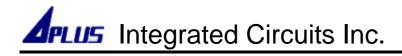

## TYPICAL APPLICATION

#### **■ MESSAGE MODE**

In fixed 1/2/4/8 message mode (C2.0), user can divide the memory averagely for 1, 2, 4 or 8 message(s). The message mode will be applied after chip reset by the Msel0 and Msel1 pin.

Please note the message should be recorded and played in same message mode, we CAN NOT guarantee the message is complete after message mode changed. For example, user recorded 8 messages in the 8-message mode, those messages can be played in 8-message mode only. If user changed to 1, 2 or 4 message mode, system will discard those messages.

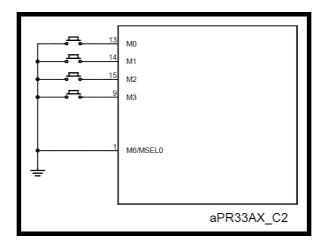

#### 8-Message Mode

The memory will be divided to 8 messages averagely when both Msel0 and Msel1 pin float after chip reset.

Ver. C 7/27 2/19/2013

## 4-Message Mode

The memory will be divided to 4 messages averagely when Msel0 pin connected to VSS and Msel1 pin float after chip reset.

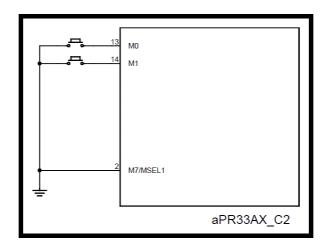

## 2-Message Mode

The memory will be divided to 2 messages averagely when Msel1 pin connected to VSS and Msel0 pin float after chip reset.

Ver. C 8/27 2/19/2013

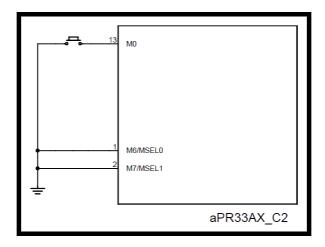

## 1-Message Mode

The memory will be for 1 message when both Msel0 and Msel1 pin connected to VSS after chip reset.

Ver. C 9/27 2/19/2013

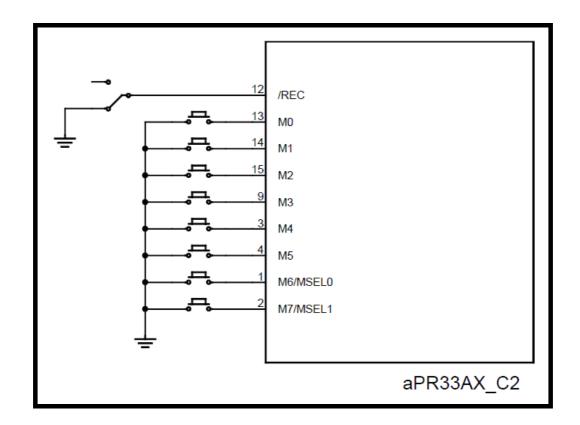

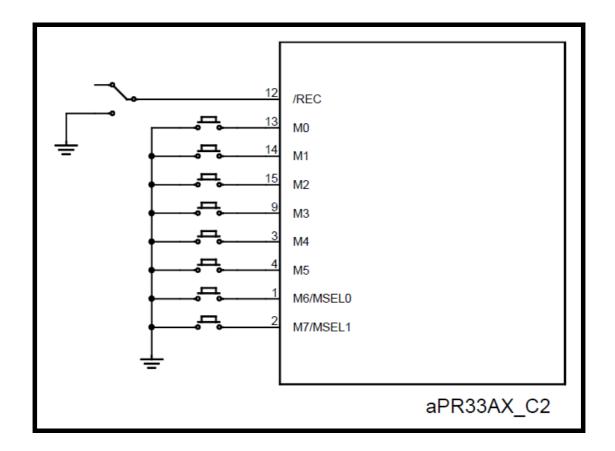

#### ■ RECORD MESSAGE

During the /REC pin drove to VIL, chip in the record mode.

When the message pin (M0, M1, M2 ... M7) drove to V<sub>I</sub> in record mode, the chip will playback "beep" tone and message record starting.

The message record will continue until message pin released or full of this message, and the chip will playback "beep" tone 2 times to indicate the message record finished.

If the message already exist and user record again, the old one's message will be replaced.

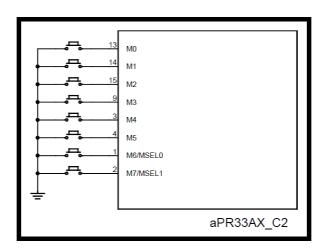

The following fig. showed a typical record circuit for 8-message mode. We connected a slide-switch between /REC pin and VSS, and connected 8 tact-switches between M0 ~ M7 pin and VSS. When the slide-switch fixed in VSS side and any tact-switch will be pressed, chip will start message record and until the user releases the tact-switch.

Note: After reset, /REC and M0 to M7 pin will be pull-up to VDD by internal resistor.

#### ■ PLAYBACK MESSAGE

During the /REC pin drove to VIH, chip in the playback mode.

When the message pin (M0, M1, M2 ... M7) drove from V<sub>I</sub>H to V<sub>I</sub>L in playback mode, the message playback starting.

The message playback will continue until message pin drove from V<sub>IH</sub> to V<sub>IL</sub> again or end of this message.

The following fig. showed a typical playback circuit for 8-message mode. We connected a slide-switch between /REC and VSS, and connected 8 tact-switches between M0 ~ M7 and VSS. When the slide-switch fixed in float side and any tact-switch will be pressed, chip will start message playback and until the user pressed the tact-switch again or end of message.

Note: After reset, /REC and M0 to M7 pin will be pull-up to VDD by internal resistor.

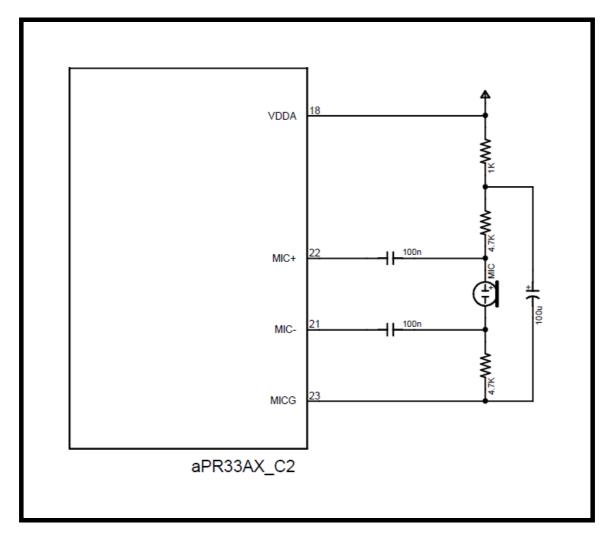

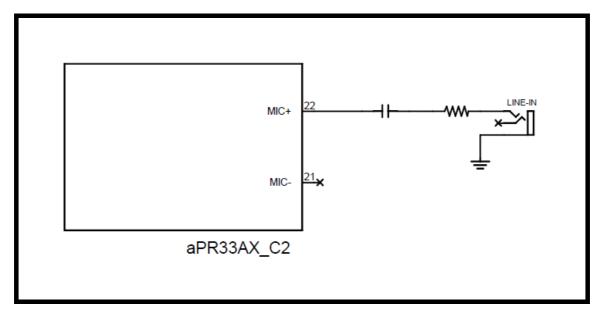

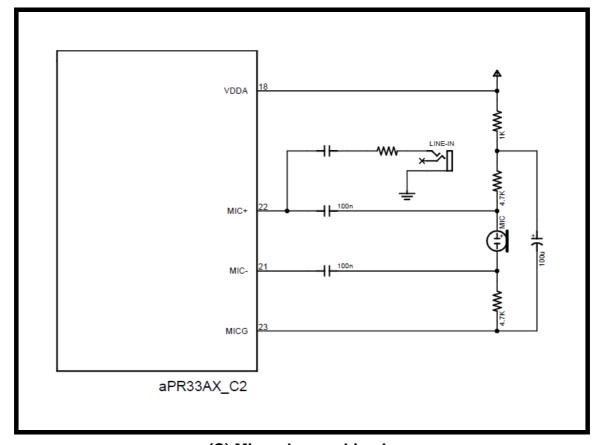

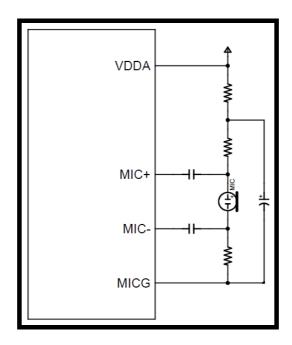

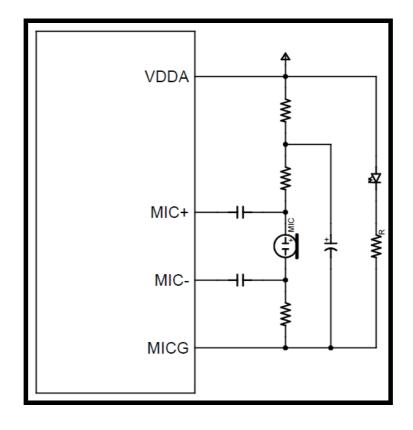

## VOICE INPUT

The aPR33A series supported single channel voice input by microphone or line-in. The following fig. showed circuit for different input methods: microphone, line-in and mixture of both.

(A) Microphone

Ver. C 2/19/2013

(B) Line-In

(C) Microphone + Line-In

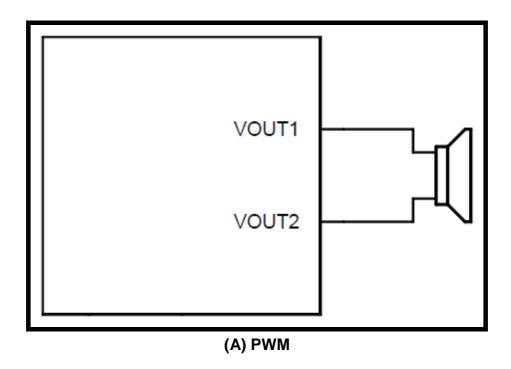

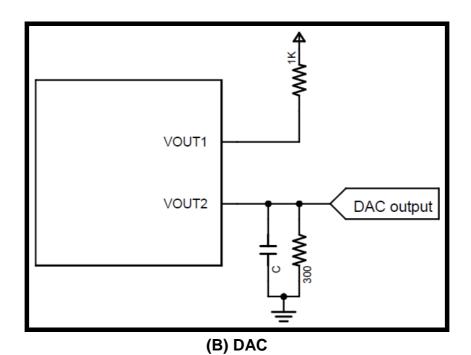

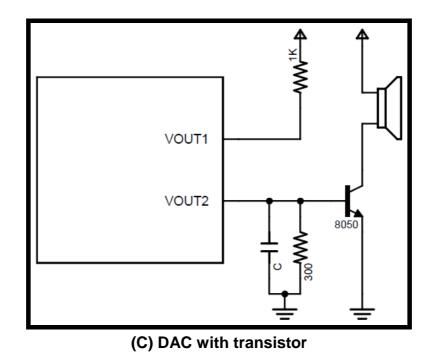

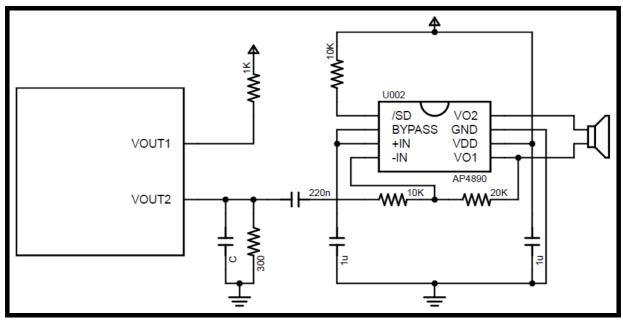

#### VOICE OUTPUT

The aPR33A series support 2 voice output mode, PWM and DAC.

The PWM mode use VOUT1 and VOUT2 pin to drive speaker directly without external components to save cost.

The DAC mode use VOUT2 pin to output current signal. User can use the signal to drive audio amplifier or mix with other components in their applications to provide larger voice volume.

The following fig. show circuit for different output methods: PWM, DAC, DAC with transistor, DAC with audio amplifier AP4890B.

Ver. C 2/19/2013

Ver. C 15/27 2/19/2013

(D) DAC with audio amplifier AP4890B

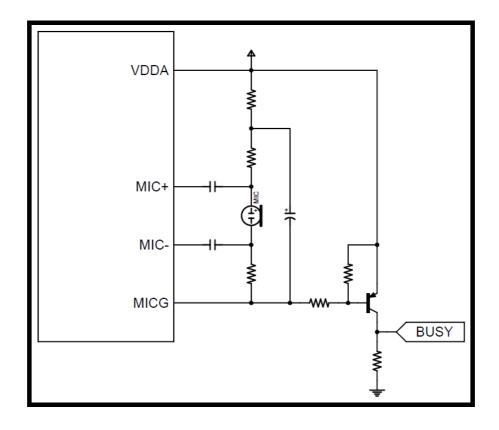

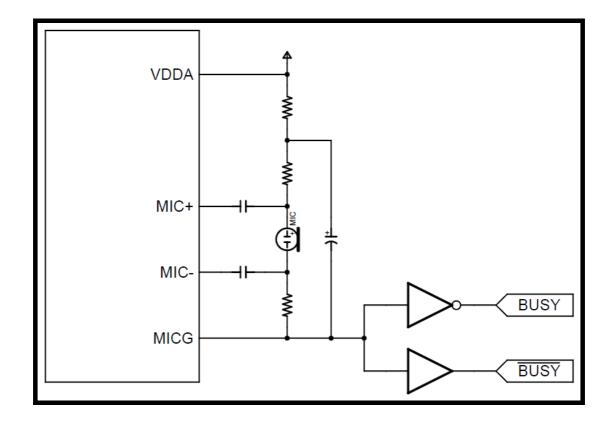

## **■** BUSY

The MICG pin will be drove to low during the message record or playback, and drove to high during idle or standby, user can detect MICG status to know chip is busy or not.

Please note it is limited for MICG pin driving current. Reference to IoH and IoL in section "**DC CHARACTERISTICS**". If MICG pin is over loading from external circuit, it will cause noise in microphone circuit.

Ver. C 2/19/2013

Below is a typical application. We add one LED to indicate IC record and playback status. We use one Resistor to limit current. And suggest R>  $470\Omega$

Ver. C 18/27 2/19/2013

Below Transistor circuit is to get higher current, larger than lohor lol.

To get best sound quality, we can use buffer or inverter to isolate MICG to avoid noise from external circuit. Driving current is provided by buffer(inverter) only.

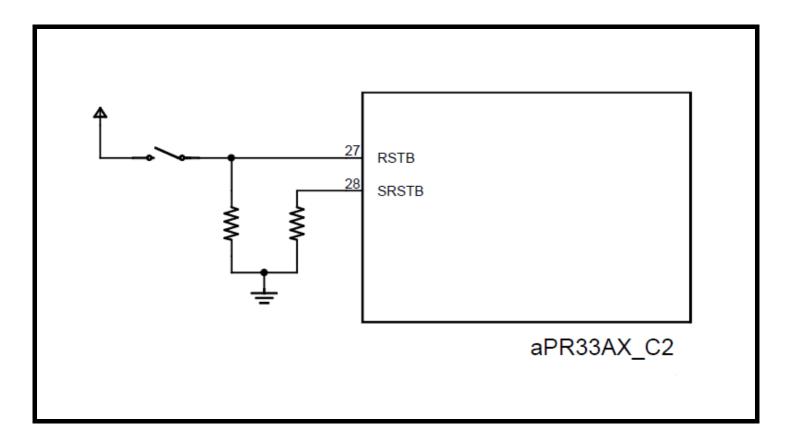

#### RESET

aPR33A series can enter standby mode when RSTB pin drive to low. During chip in the standby mode, the current consumption is reduced to IsB and any operation will be stopped, user also can not execute any new operate in this mode.

The standby mode will continue until RSTB pin goes to high, chip will be started to initial, and playback "beep" tone to indicate enter idle mode.

User can get less current consumption by control RSTB pin specially in some application which concern standby current.

Ver. C 21/27 2/19/2013

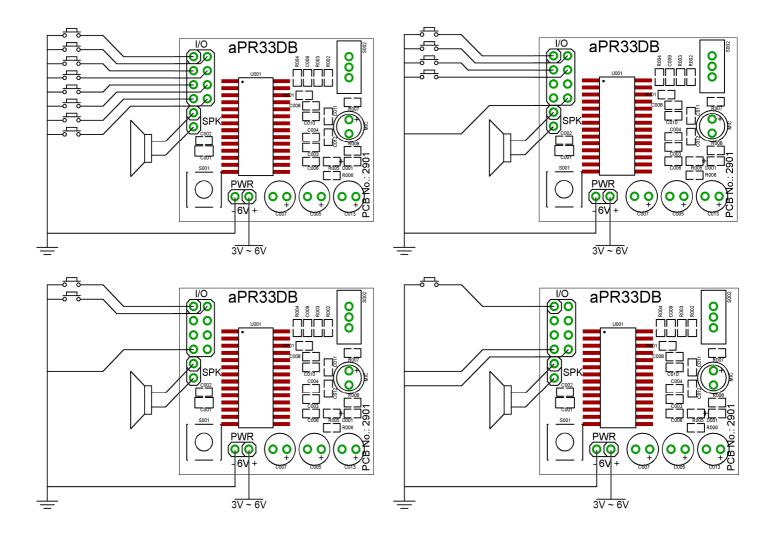

#### **■ EXAMPLE**

The aPR33DB is one of the simplest solutions for achieve fixed 1/2/4/8 message mode demo. The circuit board already includes the peripheral circuit which containing microphone. Developers only need to notice how to connect with their development environment. It can effectively decrease the time of circuit connecting & any possible mistakes. Below figure shows how to connect aPR33DB with external key in fixed 1/2/4/8 message mode:

## **■ BLOCK DIAGRAM**

**Power Management Analog Front End Digital Output Processor** PWM Power Processor Stage Pre-Amp(DE) Mic / SAGC Speaker ADC 16 bits Pre-Amp(SE) Digital DAC Audio Line Receiver **Processor Memory Controller** Non Clock Reset SRAM Volatile Circuit Generator Memory

Figure 1. Block Diagram

## ■ ABSOLUTE MAXIMUM RATINGS

| Symbol       | Rating                  | Unit                    |  |  |

|--------------|-------------------------|-------------------------|--|--|

| VDD – VSS    | -0.3 ~ +10.0            | V                       |  |  |

| Vin          | VSS-0.3 < VIN < VDD+0.3 | V                       |  |  |

| Vouт         | VSS < Vout < VDD        | V                       |  |  |

| T(Operating) | -40 ~ +85               | $^{\circ}$ C            |  |  |

| T(Junction)  | -40 ~ +125              | $^{\circ}\! \mathbb{C}$ |  |  |

| T(Storage)   | -40 ~ +125              | °C                      |  |  |

Ver. C 23/27 2/19/2013

## **■** DC CHARACTERISTICS

| Symbol    | Parameter                        |     | Тур. | Max. | Unit | Conditions                      |  |

|-----------|----------------------------------|-----|------|------|------|---------------------------------|--|

| VDD       | Operating Voltage                |     |      | 6.5  | V    |                                 |  |

| IsB       | Standby Current                  |     |      | 1    | μΑ   |                                 |  |

| IPDN      | Power-Down Current               |     | 15   | 20   | μΑ   |                                 |  |

| IOP(IDLE) | Operating Current (Idle)         |     | 20   |      | mA   | VDD = 5V                        |  |

| IOP(REC)  | Operating Current (Record)       |     | 35   |      | mA   | VDD = 5V                        |  |

| IOP(PLAY) | Operating Current (Playback)     |     | 25   |      | mA   | VDD = 5V                        |  |

| Vih       | "H" Input Voltage                | 2.5 |      |      | V    |                                 |  |

| VIL       | "L" Input Voltage                |     |      | 0.6  | V    |                                 |  |

| Іνоυт     | VOUT Current                     |     | 185  |      | mA   |                                 |  |

| Іон       | O/P High Current                 |     | 8    |      | mA   | VDD = 5V / VOH=4.5V             |  |

| loL       | O/P Low Current                  |     | 14   |      | mA   | VDD = 5V / VOH=0.5V             |  |

| Rnpio     | lanut nin null down registance   |     | 300  |      | ΚΩ   | External floating or drive low. |  |

|           | Input pin pull-down resistance   |     | 1    |      | МΩ   | External drive high.            |  |

| Rupio     | Input pin pull-up resistance     |     | 4.7  |      | ΚΩ   |                                 |  |

|           | Frequency stability              |     |      | 5    | %    | VDD = 5V ± 1.0V                 |  |

| △Fc/Fc    | Chin to chin Fraguency Variation |     |      | 5    | %    | Also apply to lot to lot        |  |

|           | Chip to chip Frequency Variation |     |      |      |      | variation.                      |  |

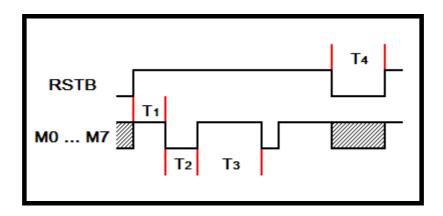

## **■** AC CHARACTERISTICS

| Symbol | Parameter          | Min. | Тур. | Max. | Unit | Conditions |

|--------|--------------------|------|------|------|------|------------|

| T1     | /CS Setup Time     | 100  |      |      | mS   | VDD=5.0V   |

| T2     | Trigger Setup Time | 16   | 1    | 1    | mS   | VDD=5.0V   |

| T3     | Trigger Hold Time  | 16   | 1    | -    | mS   | VDD=5.0V   |

| T4     | /CS Hold Time      | 100  |      |      | uS   | VDD=5.0V   |

Ver. C 25/27 2/19/2013

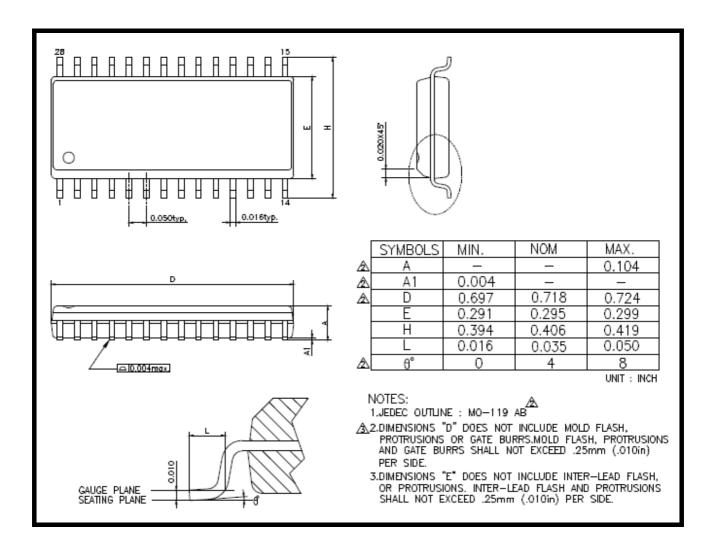

#### ■ PACKAGE INFORMATION

## **■** HISTORY

Ver. C (2013/02/08)

- Add section "VOICE OUTPUT".

- Modify code version to C2.1.

Ver. B (2013/01/17)

- Add section "BUSY".

Ver. A (2012/11/15)

- Original version data sheet for aPR33Ax C2.0.